The Power Behind the Processor: Introduction

Ever wondered what makes your smartphone snap to attention or your laptop blaze through a 4K video render? It’s all about what lies at the heart of computing—the CPU architecture. But here’s the kicker: not all processors are created equal. For decades, the tech world has been locked in a quiet, brainy battle between two competing philosophies: RISC and CISC. These acronyms represent two fundamentally different approaches to how computers understand and execute instructions.

So, why should you care about RISC vs CISC: Understanding CPU Architecture Simply? Because behind the scenes, this rivalry influences the speed, efficiency, cost, and even the battery life of your devices. Whether you’re a tech enthusiast, student, or future systems designer, knowing how these architectures differ is like holding the blueprint to digital intelligence.

Let’s dive deep, not just into theory, but into how these two giants shape our digital lives.

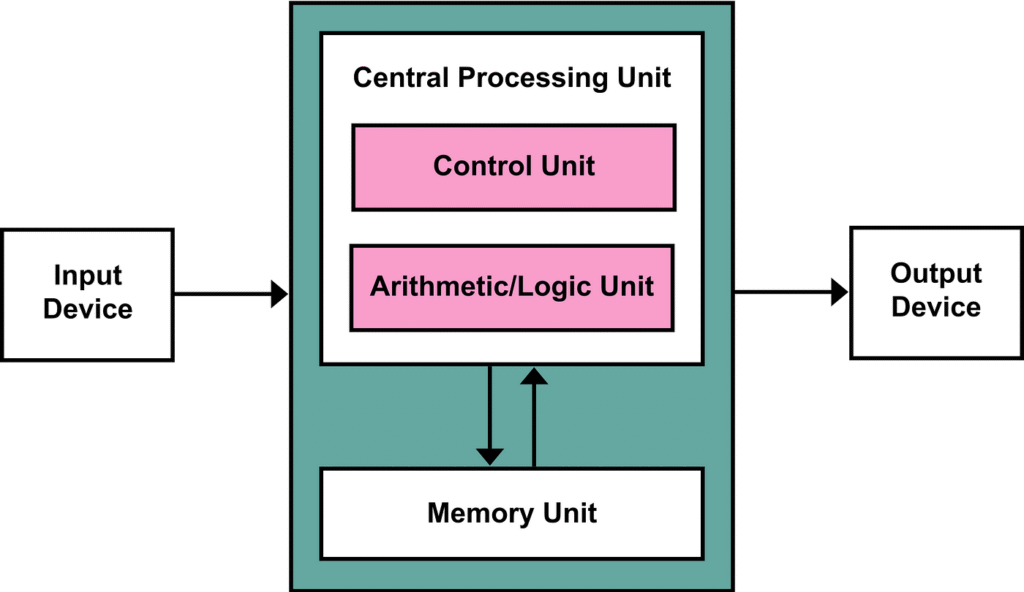

Understanding CPU Architecture

Every computing system is powered by a CPU, and at the very core of every CPU is its architecture. This architecture defines how the processor interprets instructions, manipulates data, communicates with memory, and ultimately, gets things done.

Think of the CPU architecture like the grammar rules in a language. Just like sentences are constructed from words, programs are built from instructions. And those instructions must follow specific patterns to be understood.

There are countless ways to organize a CPU’s instruction set, but over the years, two dominant styles have emerged—RISC (Reduced Instruction Set Computing) and CISC (Complex Instruction Set Computing). Each one is built on distinct philosophies with different trade-offs.

The Fundamental Concepts of CPU Design

Designing a CPU is an elegant dance between complexity, cost, and performance. The choices made at the design level determine whether the chip will be nimble, powerful, or energy-efficient—or maybe none of the above.

When designing a CPU, engineers must answer questions like:

- Should each instruction do more or less?

- Is it better to simplify the hardware or the software?

- How do we balance performance with energy usage?

These decisions culminate in what we call an Instruction Set Architecture (ISA)—the bridge between hardware and software, the dictionary that tells the processor what to do.

And this is where the showdown begins: RISC vs CISC.

Background on Instruction Sets

Before we step into the ring, let’s demystify instruction sets.

Instruction sets are the vocabulary a CPU uses to communicate with software. For example, telling the CPU to add two numbers or move data from one location to another. Some CPUs use a vast vocabulary with complex instructions, while others prefer fewer, simpler words to get the job done.

This division is where RISC and CISC part ways.

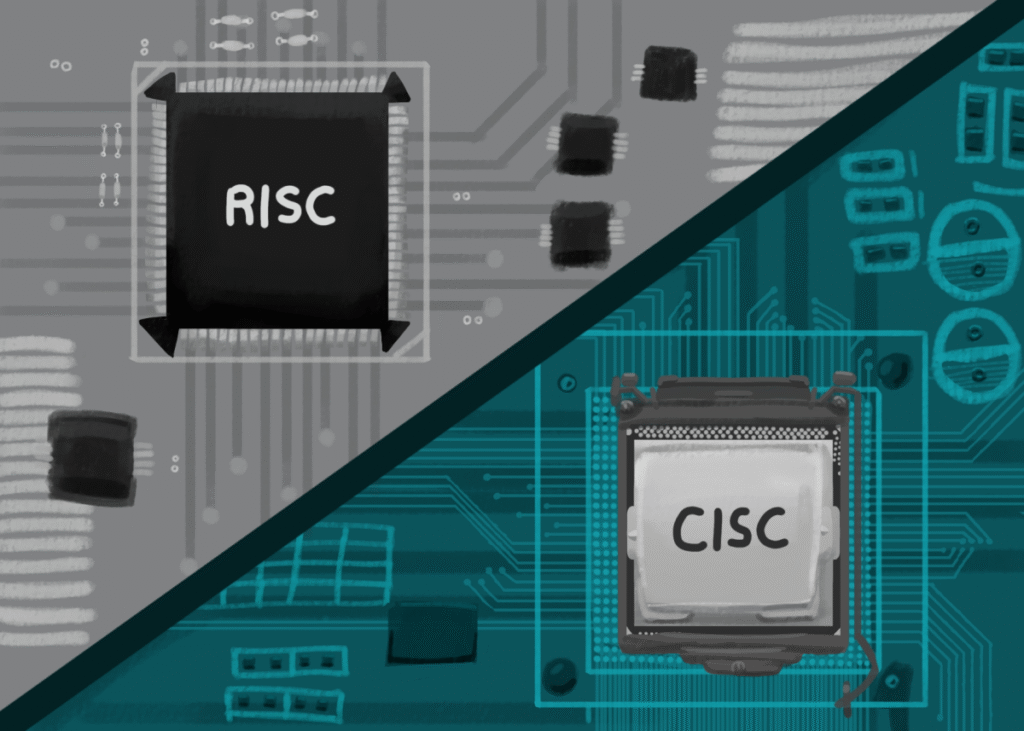

RISC vs CISC: Understanding CPU Architecture Simply

Let’s clear the fog with a simple analogy. Imagine building a bookshelf.

- CISC is like having a single tool that can measure, cut, sand, and screw in one go—sounds efficient, but the tool is complex and slower to handle.

- RISC, on the other hand, is like having a set of specialized, easy-to-use tools—each does one job, but very quickly.

Now apply that to processors. CISC CPUs like Intel’s x86 architecture pack more powerful instructions, whereas RISC chips like ARM break tasks into smaller, faster chunks. The result? CISC may need fewer instructions per task, but each instruction takes longer. RISC might need more steps, but each one is lightning fast.

Both strategies aim to reach the same destination. The debate is about the best route to take.

Differences Between RISC and CISC Explained

Here’s how they differ, side by side:

| Feature | RISC | CISC |

|---|---|---|

| Instruction Complexity | Simple, single-cycle | Complex, multi-cycle |

| Number of Instructions | Fewer | Many |

| Execution Time per Instruction | Faster | Slower |

| Hardware Complexity | Lower | Higher |

| Power Consumption | Lower | Higher |

| Code Size | Larger | Smaller |

| Pipelining Support | Easy | Complicated |

Each has its strengths, and each shines in different scenarios. The choice between them depends on the goals of the hardware and software engineers.

RISC: Reduced Instruction Set Computing

RISC chips focus on simplicity and speed. They use a limited set of instructions, each executed in a single clock cycle. The architecture is designed for pipelining—executing multiple instructions simultaneously by overlapping steps.

This makes RISC highly suitable for:

- Mobile devices

- Embedded systems

- Low-power, high-efficiency tasks

With fewer instructions, compilers and programmers have to work a bit harder, but the streamlined performance often makes up for it.

CISC: Complex Instruction Set Computing

CISC processors, in contrast, aim to do more with less. Their rich instruction sets allow a single command to perform multiple operations. This reduces the number of instructions in a program, which can shrink code size and improve memory efficiency.

CISC excels in:

- Desktop environments

- General-purpose computing

- Legacy compatibility

Though complex, these CPUs can deliver excellent performance where memory is limited and backward compatibility is crucial.

Advantages of RISC Architecture

Simplicity = Speed: With fewer instructions, execution is lightning fast.

Lower Power Consumption: Ideal for battery-powered devices.

Cost Efficiency: Simpler design means cheaper to produce.

Better Performance for Modern Apps: Especially those that rely on multitasking.

Advantages of CISC Architecture

Compact Code: Less memory usage due to fewer instructions.

Legacy Support: Compatible with older software, which is vital for enterprise use.

Instruction Efficiency: Fewer lines of code needed for complex operations.

Ease of Programming: More functionality per instruction can simplify some development tasks.

Key Features of RISC vs CISC

When it comes to distinguishing between RISC and CISC, the key features lie in how they process and manage instructions at the hardware level.

RISC Key Features:

- Load/Store Architecture: Memory access is limited to specific instructions.

- Uniform Instruction Format: Simplifies decoding and enhances speed.

- Fixed-Length Instructions: Easier to pipeline and predict.

- General-Purpose Registers: A larger set of registers reduces memory access.

CISC Key Features:

- Microprogrammed Control Units: Enables complex instructions.

- Variable-Length Instructions: Allows more flexibility per instruction.

- Fewer Registers: Relies more heavily on memory.

- Instruction Decoding Complexity: More work for the CPU to interpret instructions.

Together, these features dictate how quickly, efficiently, and powerfully a processor performs—each shining in different domains.

Comparing Instruction Sets in RISC and CISC

Instruction sets are the “language” a CPU understands. Let’s compare them more closely.

RISC Instruction Set:

- Focused on simplicity and speed.

- Instructions like ADD, LOAD, and STORE are executed in a single clock cycle.

- Requires more lines of code but each line is optimized for fast execution.

CISC Instruction Set:

- Instructions like MULT (multiply) or MEMCPY(copy memory) perform multiple operations in one instruction.

- Reduces the number of instructions per program, but increases complexity and execution time.

In software terms, writing for RISC is like spelling everything out step by step. With CISC, you can use shortcuts—but at the cost of increased CPU decoding time.

Performance Considerations of RISC and CISC

Performance isn’t just about raw speed—it’s about how efficiently a processor handles real-world tasks.

- RISC excels in environments requiring quick response times and low power usage (smartphones, wearables).

- CISC shines where software optimization is crucial and backward compatibility is non-negotiable (desktop PCs, servers).

Let’s break it down:

| Scenario | RISC Advantage | CISC Advantage |

|---|---|---|

| Real-Time Systems | ✅ | ❌ |

| Complex Software | ❌ | ✅ |

| Battery-Dependent Devices | ✅ | ❌ |

| Multithreaded Performance | ✅ | ✅ |

| Legacy App Support | ❌ | ✅ |

There’s no universal winner—performance depends on the context.

Instruction Execution in RISC CPUs

Execution in RISC is like an assembly line in a high-speed factory. Each worker (instruction) knows exactly what to do and completes its task in perfect synchronization with the others.

- One instruction per clock cycle.

- Minimal decoding time due to instruction uniformity.

- Pipeline-friendly: Instructions are neatly organized into fetch, decode, execute, memory access, and write-back stages.

This precision makes RISC an attractive choice for multi-core processors and systems that prioritize efficiency over complexity.

Instruction Execution in CISC CPUs

CISC processors work more like multi-function machines. They take fewer steps overall, but each step might involve multiple sub-tasks.

- Single instruction performs multiple actions.

- Microcode translation allows rich operations, but slows execution.

- Complex decoding adds latency but supports powerful software needs.

For instance, a CISC instruction might load two values, multiply them, and store the result in one go—great for code density, but slower to execute than multiple RISC steps.

Processor Architecture Evolution

The landscape of CPU design has evolved dramatically—and interestingly, RISC and CISC have started to borrow ideas from each other.

- Modern CISC processors (like Intel’s Core series) internally break complex instructions into RISC-like micro-operations.

- Modern RISC chips (like Apple’s M1) now integrate features previously exclusive to CISC, such as speculative execution and out-of-order processing.

This fusion reflects a central truth in engineering: pure theory bends to practical demands. The hybridization is proof that neither RISC nor CISC holds absolute dominance—they evolve to meet users’ real needs.

Impact of RISC vs CISC on Software Development

Software doesn’t run in isolation. The underlying CPU architecture influences everything from compiler design to runtime performance.

RISC’s impact on software:

- More work for compilers: They must generate longer instruction sequences.

- Predictable performance: Developers can better anticipate execution times.

- Code readability: Easier to debug at low levels.

CISC’s impact:

- Efficient memory usage: Great for embedded systems with limited RAM.

- Support for legacy code: Allows old software to thrive.

- Higher-level abstraction: Simplifies development in some languages.

Choosing between them affects more than just hardware—it ripples all the way into software architecture and maintenance strategies.

Energy Usage Differences: RISC Power Efficiency

Power consumption is a big deal, especially in a mobile-first world. RISC shines here.

- Simpler circuitry = lower voltage requirements.

- Shorter instruction paths = less heat and wasted energy.

- Idle energy savings: Better power gating and sleep modes.

Companies like ARM Holdings have capitalized on this with CPUs that deliver long battery life without sacrificing performance. It’s no surprise nearly 90% of smartphones use RISC-based processors today.

Energy Usage Differences: CISC Processing Demands

CISC processors tend to consume more energy, especially during high-load tasks.

- Complex instructions = more transistors active.

- Longer decoding times = more cycles per task.

- Greater heat output: Requires better cooling systems.

That said, CISC designers have added modern power-saving techniques (like Intel’s Turbo Boost) to minimize the gap. Still, for always-on, low-power environments, RISC remains king.

Programming Models Compared: RISC vs CISC

Programming for each architecture requires a different mindset.

- RISC encourages clarity and modularity.

- CISC allows abstraction and brevity.

Example:

To multiply two numbers and store the result:

- RISC: Load → Multiply → Store (3 steps)

- CISC: Multiply and Store (1 step)

For developers writing at the assembly level or building real-time systems, RISC offers more control. For those relying on high-level languages, the impact may be abstracted—unless optimization is the goal.

Final Thoughts: Choosing Between RISC and CISC in a Modern World

As we wrap up this deep dive into RISC vs CISC: Understanding CPU Architecture Simply, one truth becomes crystal clear—there’s no one-size-fits-all answer. Each architecture is a product of thoughtful design, real-world trade-offs, and evolving needs.

RISC champions simplicity, speed, and power efficiency, making it the go-to for smartphones, tablets, wearables, and embedded systems where battery life and efficiency reign supreme. Its streamlined approach allows developers to fine-tune performance and engineers to build lean, responsive hardware that quietly powers billions of devices every day.

CISC, on the other hand, stands as the workhorse of legacy compatibility and software richness. Its strength lies in its ability to execute complex instructions with fewer lines of code, conserving memory and making programming easier at a higher level. From personal computers to enterprise-grade servers, CISC processors continue to drive performance where deep software ecosystems demand robust backward compatibility.

But here’s the fascinating part: the line between them is blurring. Today’s CPUs often combine the best of both worlds—the minimalism of RISC with the complexity of CISC, crafting hybrid microarchitectures that adapt to both modern software and future demands.

So, whether you’re a tech enthusiast building your first system, a student stepping into the world of computer engineering, or a developer curious about what makes your code tick, understanding this architectural tug-of-war gives you a powerful edge.

In the end, it’s not just RISC vs CISC—it’s about making smart choices in a world where every nanosecond and every watt matters. Choose wisely, think efficiently, and always stay curious about what powers the tools you trust.